Example Projects

This page provides a set of sample projects for use with SmartSim. They are provided as ".zip" archives containing component and project files, which must be extracted before use.

To open these projects, run SmartSim and use File - Open Project, and find the project file (ending in ".ssp").

These examples are intended primarily for demonstrating SmartSim's capabilities rather than teaching digital logic.

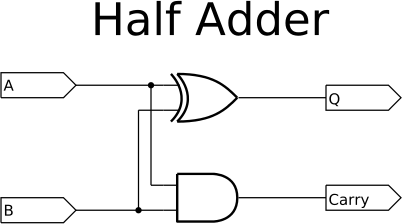

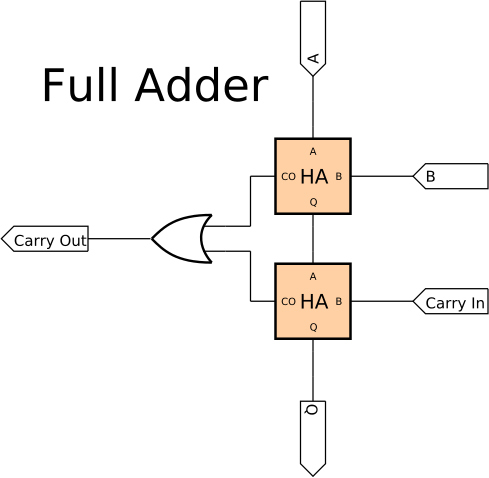

4 Bit Addition

This example shows how to perform binary addition using half-adders and full-adders.

| Download |

|---|

| Zip Archive |

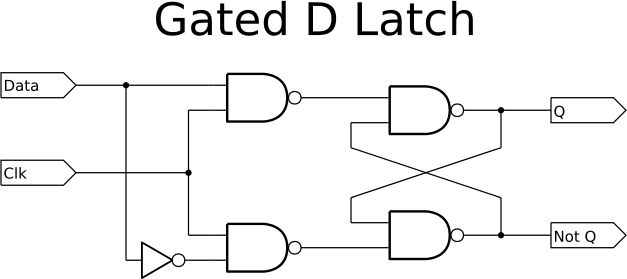

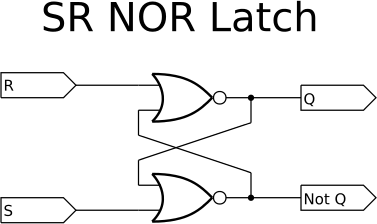

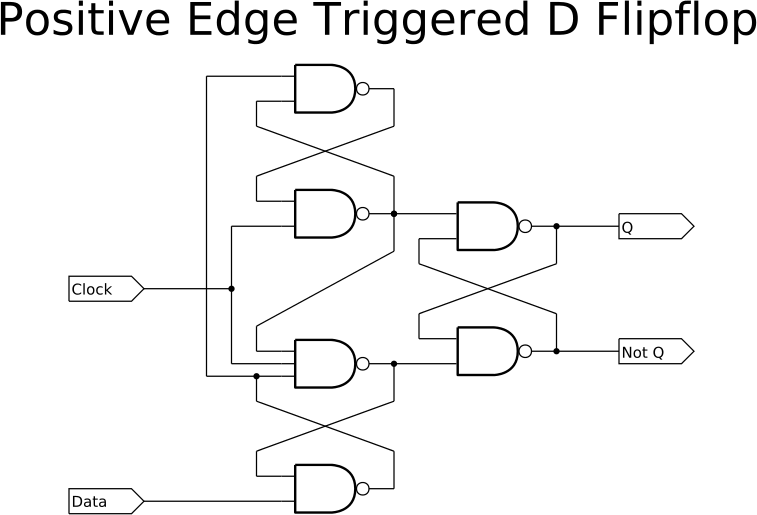

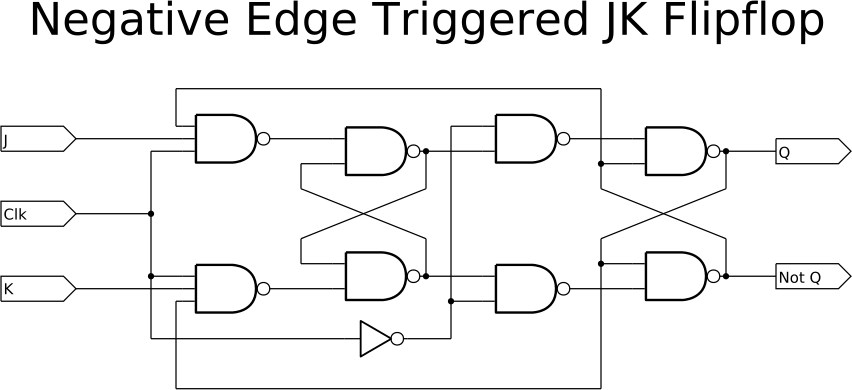

Flipflop Collection

This is a collection of 1 bit memory storage components, known as flipflops. It demonstrates the SR NOR Latch, D Latch, Positive Edge Triggered D Flipflop, and Negative Edge Triggered JK Flipflop

| Download |

|---|

| Zip Archive |

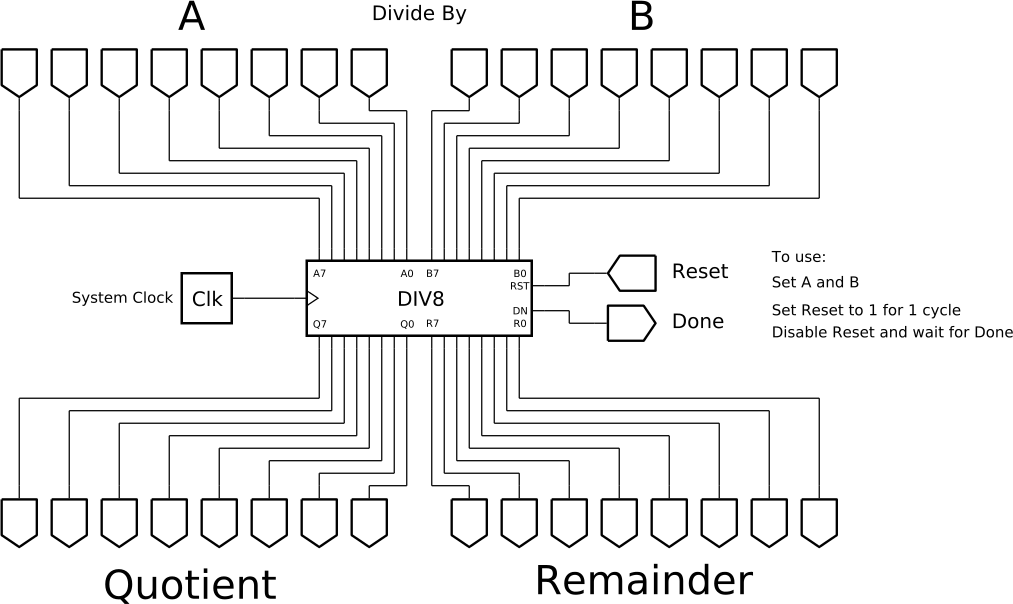

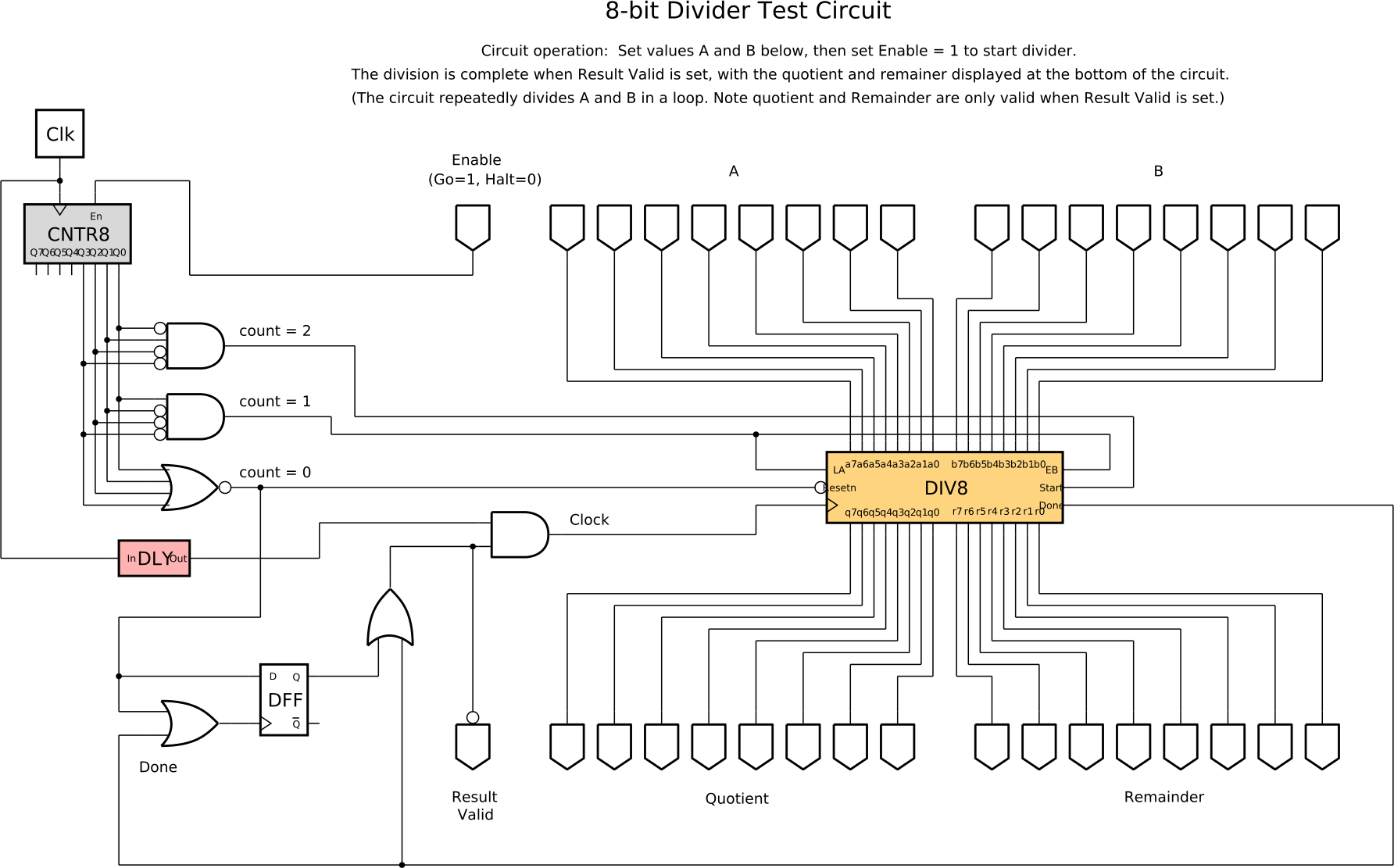

8 Bit Divider

This is a division circuit I made early on in the development of SmartSim.

| Download |

|---|

| Zip Archive |

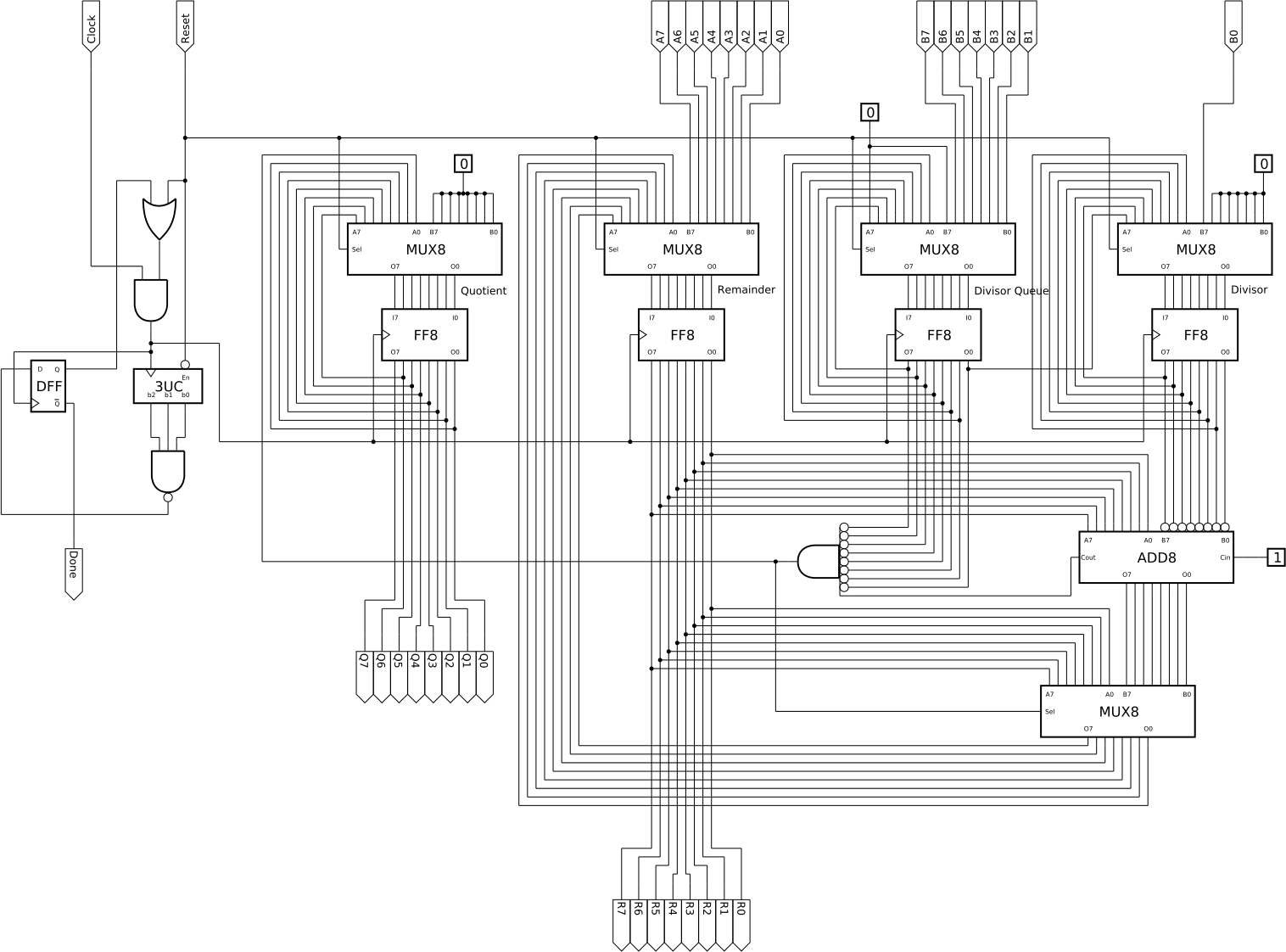

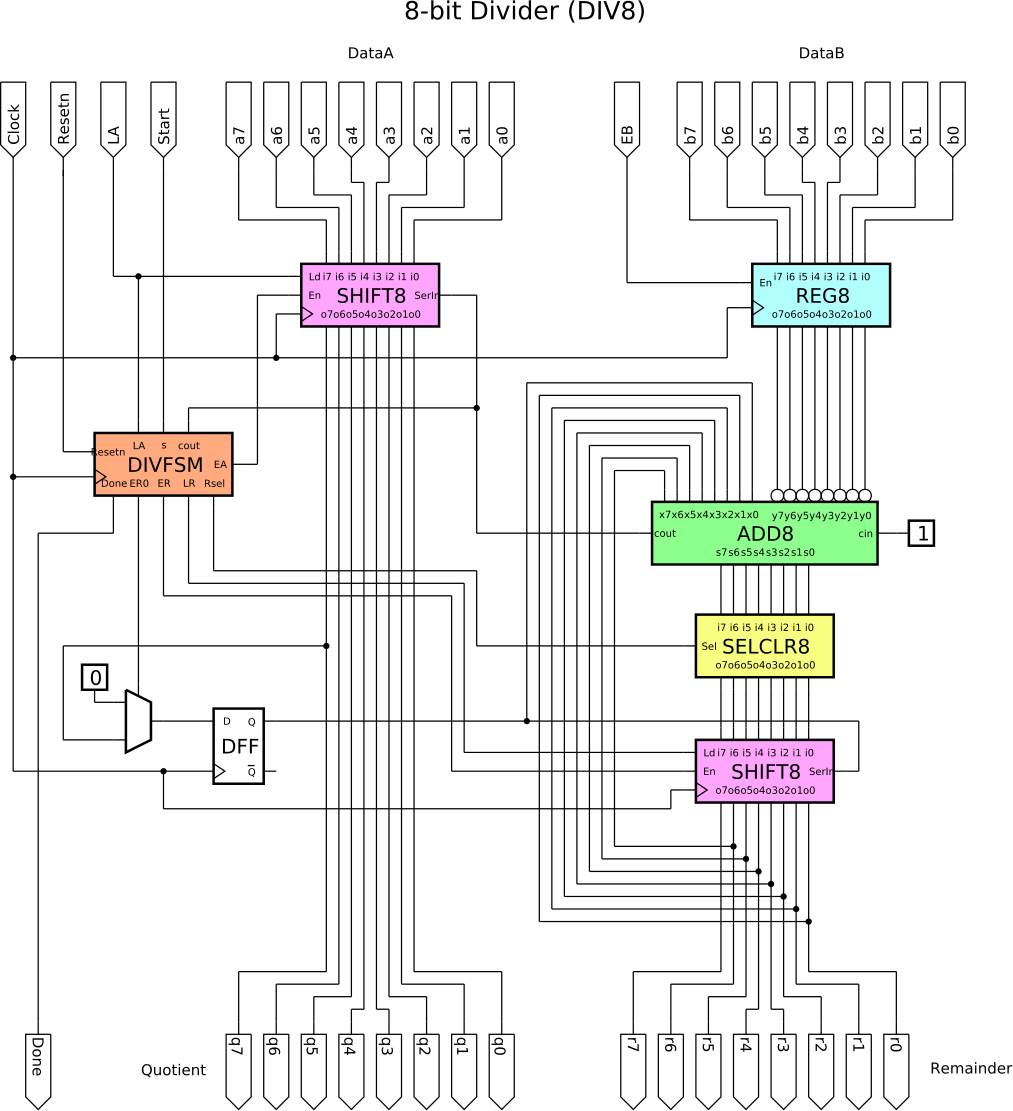

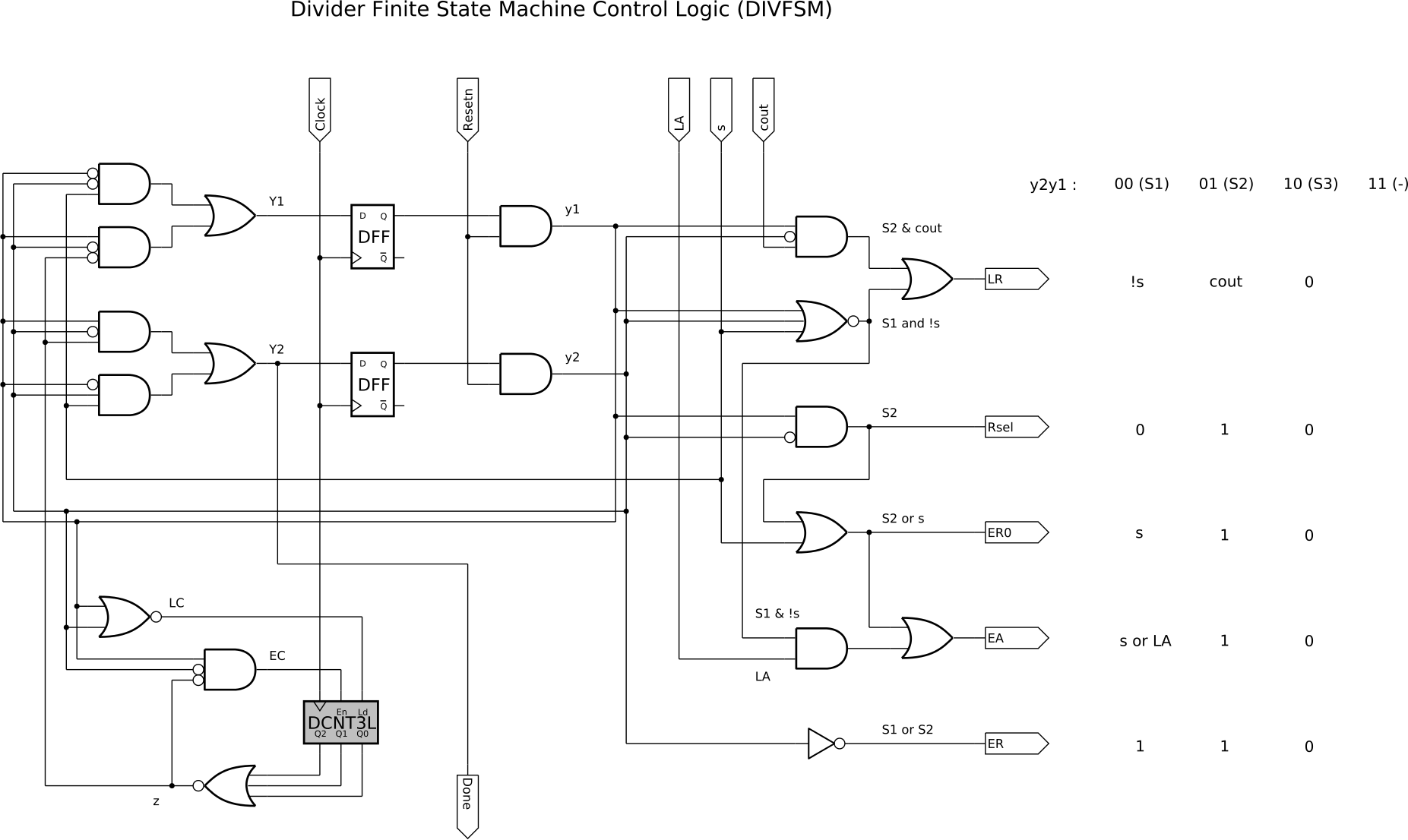

8 Bit Division Using Finite State Machine.

This is another divider, but it uses a slightly different approach utilising a finite state machine.

| Download |

|---|

| Zip Archive |

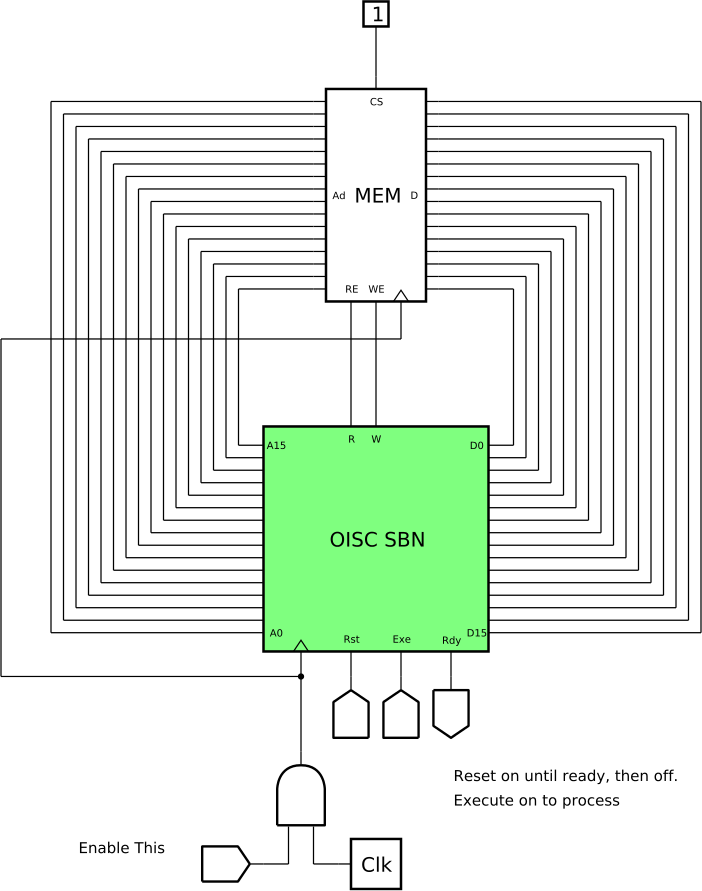

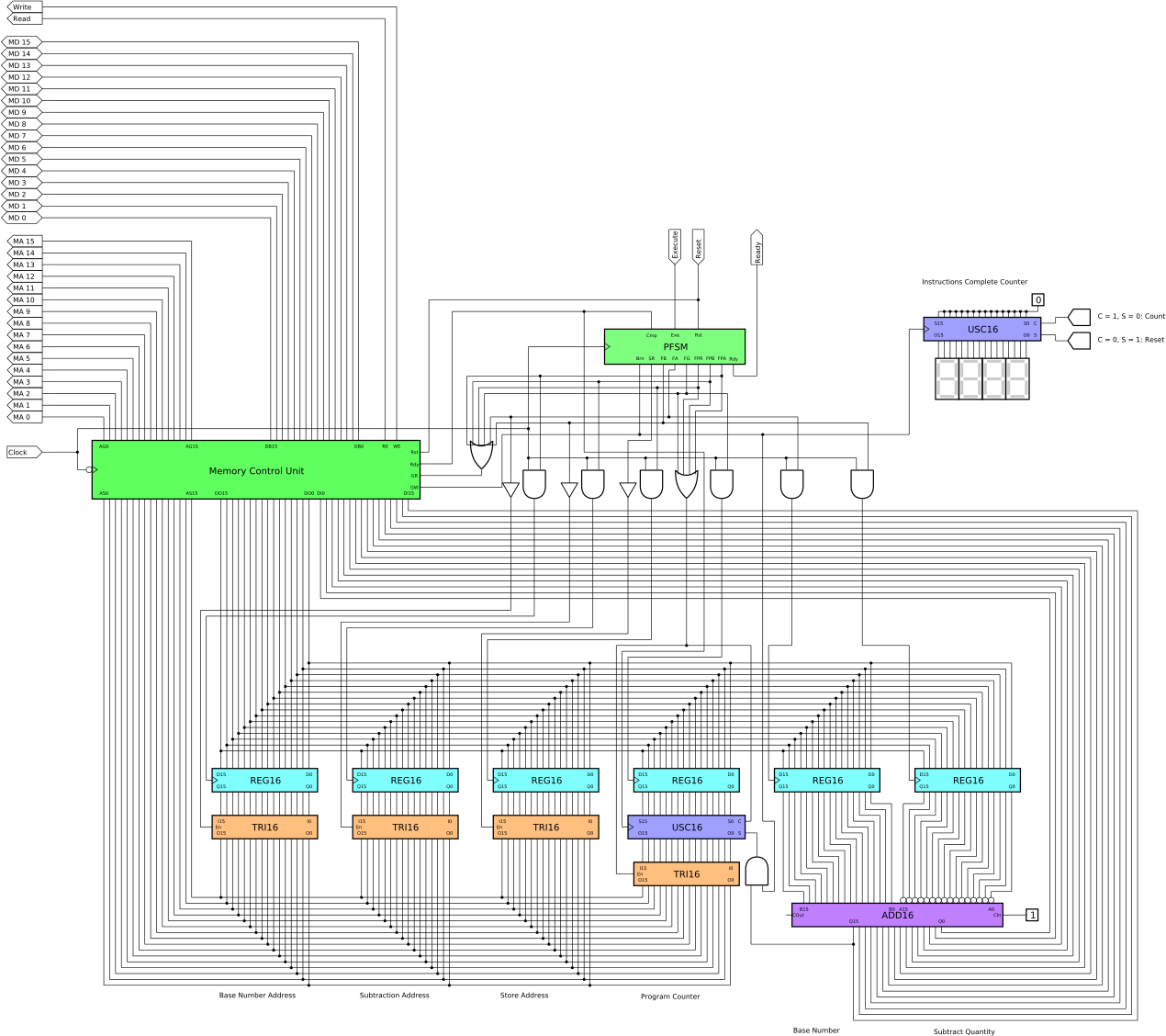

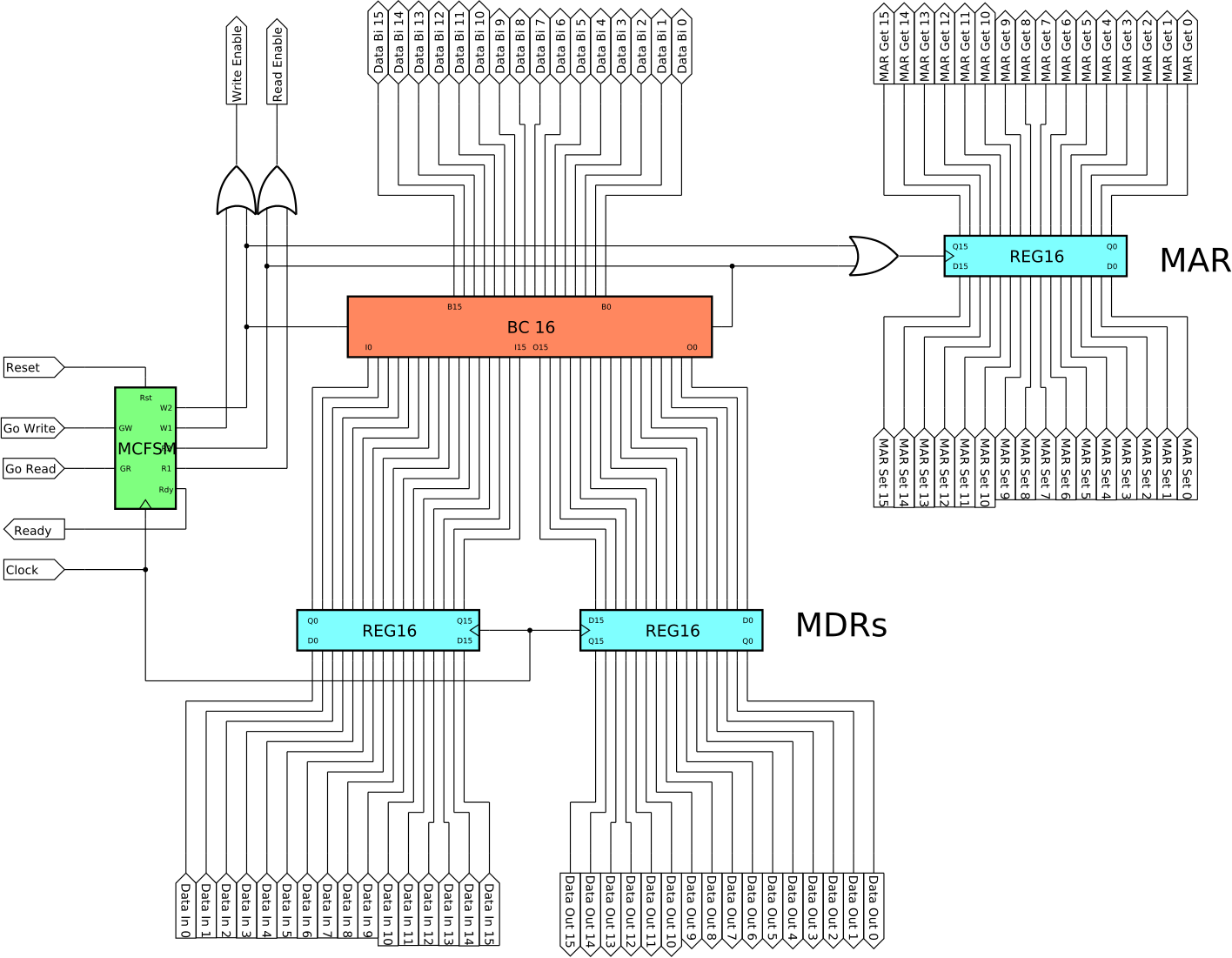

16 Bit One Instruction Set Computer (OISC)

This is a minimalistic turing complete processor, which only performs one instruction, and thus does not require an opcode. It is a Subtract and Branch if Negative (SBN) processor, which means that it subtracts two numbers and jumps to an instruction if the result is negative. Also included are two programs for the processor: count in 11s, and generate Fibonacci numbers. These programs are selectable by adjusting the memory chip in the circuit and finding a ".bin" file.

To learn more about one instruction set computers, visit the OISC Wikipedia article.

| Download |

|---|

| Zip Archive |

Copying

All these circuits are released to the public domain, meaning you can freely edit and distribute these files.